by

## MARIO NAKAZAWA

(Under the direction of David K. Lowenthal)

#### **ABSTRACT**

Large scale scientific applications can take a significant amount of time when run sequentially. Parallelism is one way to reduce their execution time. Two key problems in efficiently running a program in parallel on a distributed memory architecture are (1) scheduling the application and (2) distributing the work so as to simultaneously minimize the time spent in communication and in local processing on each node. The input to these programs can be very large, and they are increasingly likely to run on a heterogeneous architecture—both situations make it likely that they will need to access the disk while running, incurring I/O costs. Ignoring these costs can greatly degrade performance because they are typically an order of magnitude more expensive than message passing latencies or cache misses.

We determined using a simulator that I/O-awareness in gang scheduling can increase throughput and reduce turnaround times of applications by as much as a factor of three. This result motivated us to develop a runtime system that solves the data distribution problem for applications running on a heterogeneous cluster of machines. This dissertation describes two components of this system we implemented: (1) the search mechanism, and (2) the computational model it uses to evaluate each candidate distribution. An exhaustive search is computationally intractable, so we simplified the problem by assuming a monotonic relationship between a data distribution and the resulting application execution time. Our search algorithm, which we call GBS, is optimal in solving this simplified problem. We also developed a computation model called MHETA, which is used as an evaluation function by the search algorithm. The model integrates an application's structural information and instrumented measurements to generate a predicted execution time given an input distribution. In our experimental test bed consisting of four scientific applications on 17 emulated architectures, GBS on average produces distributions within 5% of the optimal within one second of running. We also show that MHETA is on average at least 97% accurate in its predictions, indicating that the GBS algorithm (with MHETA) successfully finds effective data distributions for a parallel application running on a heterogeneous cluster on the fly.

INDEX WORDS: Computation models, Data distributions, Scheduling, I/O Awareness, Heterogeneous architectures

# I/O CONSIDERATIONS IN EFFICIENT HETEROGENEOUS DATA DISTRIBUTIONS

by

## MARIO NAKAZAWA

B.A. University of Pennsylvania, 1994

A Dissertation Submitted to the Graduate Faculty of The University of Georgia in Partial Fulfillment of the

Requirements for the Degree

DOCTOR OF PHILOSOPHY

ATHENS, GEORGIA

2005

© 2005

Mario Nakazawa

All Rights Reserved

# I/O CONSIDERATIONS IN EFFICIENT HETEROGENEOUS DATA DISTRIBUTIONS

by

# MARIO NAKAZAWA

Approved:

Major Professor: David K. Lowenthal

Committee: Suchendra Bhandarkar

Eileen Kraemer

Electronic Version Approved:

Maureen Grasso Dean of the Graduate School The University of Georgia May 2005

## ACKNOWLEDGMENTS

I would like to thank my wife Jeanne for her love and support. She knew what she was getting into when we got married in the middle of the dissertation writing process, and her faith in my abilities never wavered. We make a great team.

I also appreciate the efforts of my committee members in helping me correct and write this dissertation. I feel more confident in my future endeavors by their efforts to extend my knowledge of the material and push me to the limits of what I know.

Finally, I wish to thank my adviser Dr. Lowenthal for asking me to work with him those many years ago when I was looking for a topic to investigate. He was always ready and willing to help me in my writing and critical thinking, and he was an invaluable guide to bring my ideas into fruition.

# TABLE OF CONTENTS

| Pag                                             | зe  |

|-------------------------------------------------|-----|

| KNOWLEDGMENTS                                   | iv  |

| T OF FIGURES                                    | 'ii |

| T OF TABLES                                     | ix  |

| APTER                                           |     |

| 1 Introduction                                  | 1   |

| 1.1 Issues in Parallelizing Sequential Programs | 3   |

| 1.2 Dividing the Work                           | 4   |

| 1.3 I/O COSTS AND DATA ASSIGNMENT               | 5   |

| 1.4 Dissertation Structure                      | 8   |

| 2 Related Work                                  | 9   |

| 2.1 Modeling                                    | 9   |

| 2.2 Data Distribution                           | 1   |

| 2.3 Out-of-core Parallel Programming            | 2   |

| 2.4 Non-dedicated and Heterogeneous Computing   | 6   |

| 3 I/O-Awareness in Gang Scheduling              | 8   |

| 3.1 GANG SCHEDULING OVERVIEW                    | 9   |

| 3.2 Implementation                              | 21  |

| 3.3 Gang Scheduling Performance                 | 2   |

| 3.4 CONCLUSION                                  | 9   |

| 4     | 1/O C  | OSTS IN SEARCHING FOR A DATA DISTRIBUTION       | 40  |

|-------|--------|-------------------------------------------------|-----|

|       | 4.1    | PROBLEM COMPLEXITY                              | 41  |

|       | 4.2    | PROBLEM FORMALIZATION                           | 42  |

|       | 4.3    | THE SEARCH ALGORITHMS                           | 44  |

| 5     | Predi  | CTING EXECUTION TIME USING COMPUTATIONAL MODELS | 52  |

|       | 5.1    | COMPUTATION MODEL FRAMEWORK                     | 52  |

|       | 5.2    | EXTRACTING MHETA COMPONENTS                     | 55  |

|       | 5.3    | MHETA IMPLEMENTATION                            | 61  |

| 6     | PERFO  | ORMANCE                                         | 73  |

|       | 6.1    | GENERAL EXPERIMENTAL SETUP                      | 73  |

|       | 6.2    | MEASURING MHETA ACCURACY                        | 75  |

|       | 6.3    | PERFORMANCE ANALYSIS OF THE SEARCH ALGORITHMS   | 82  |

|       | 6.4    | GENERAL CONCLUSIONS                             | 89  |

| 7     | Conc   | LUSION AND FUTURE WORK                          | 90  |

|       | 7.1    | FUTURE WORK                                     | 92  |

| Bibli | OGRAPI | HY                                              | 95  |

| APPEI | NDIX   |                                                 |     |

| A     | Сомр   | LEX ANALYSIS OF SCIENTIFIC APPLICATIONS         | 103 |

# LIST OF FIGURES

| 1.1  | The composition the complete runtime system                                    | 7  |

|------|--------------------------------------------------------------------------------|----|

| 3.1  | A job inserted into a gang scheduler's trace matrix                            | 22 |

| 3.2  | Placing a job into multiple rows in a gang scheduler's trace matrix            | 30 |

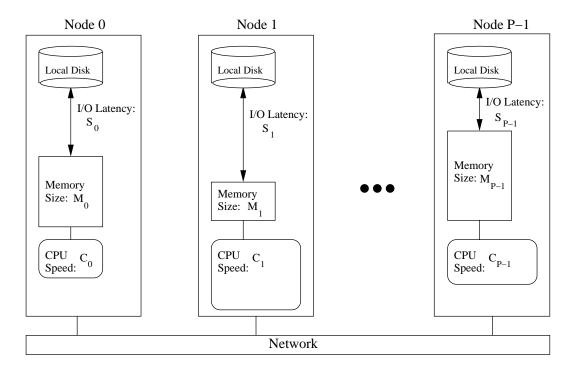

| 4.1  | The composition of the heterogeneous architecture emulated for our experiments | 41 |

| 4.2  | The Generalized Binary Search Algorithm                                        | 45 |

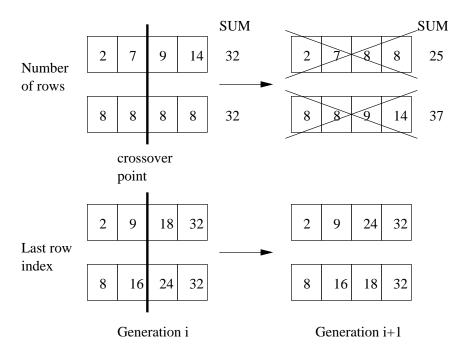

| 4.3  | Two different resentations for genetic algorithms                              | 48 |

| 4.4  | Simulated annealing algorithm pseudocode                                       | 50 |

| 5.1  | A sample parallization of a sequential program                                 | 54 |

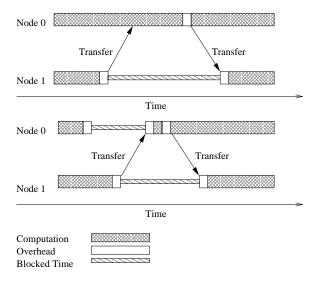

| 5.2  | Examples of communication events                                               | 57 |

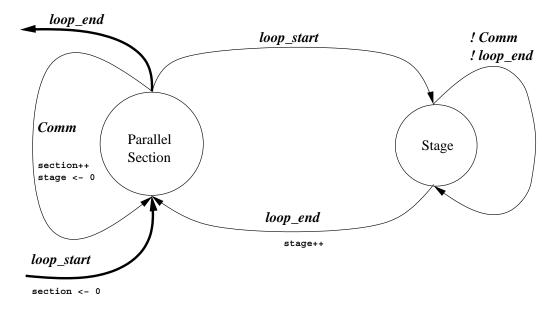

| 5.3  | The simple state diagram of the instrumenting preprocessor                     | 58 |

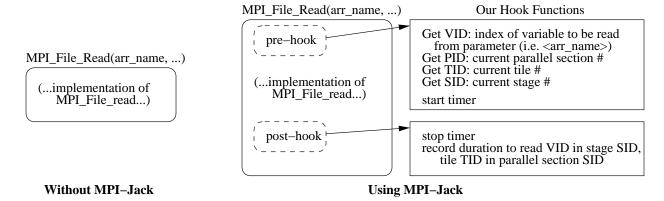

| 5.4  | A graphical example of how MPI Jack is used to extract timing information      | 59 |

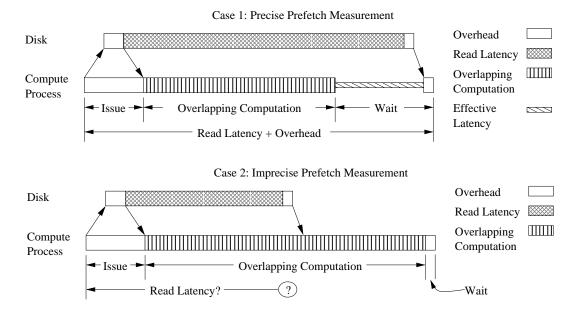

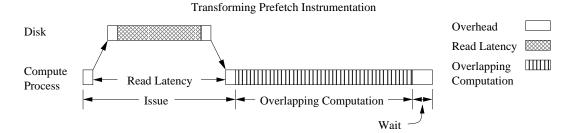

| 5.5  | Problems when trying to instrument prefetching code                            | 60 |

| 5.6  | Solution to instrumenting prefetch code                                        | 61 |

| 5.7  | A simple transformation to enable prefetching.                                 | 64 |

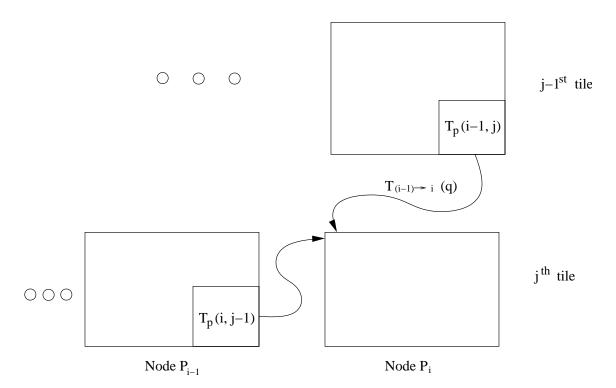

| 5.8  | A graphical description of a reduction communication event                     | 65 |

| 5.9  | The behavior of pipelined applications                                         | 67 |

| 5.10 | Blocked time for node $P_i$ to start its $j^{th}$ tile                         | 71 |

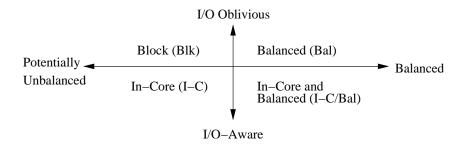

| 6.1  | The spectrum of data distributions that we tested                              | 76 |

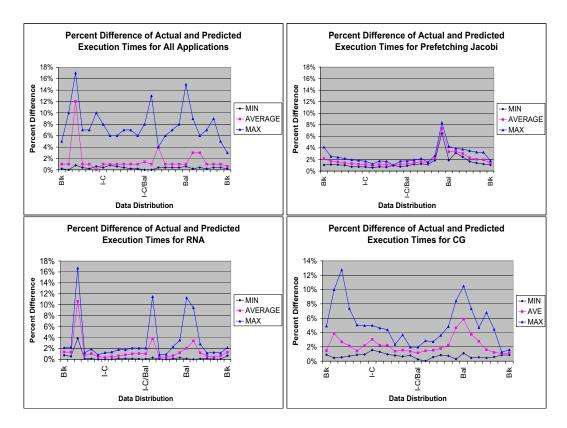

| 6.2  | The minimum, average and maximum percentage difference between the predicted   |    |

|      | and actual execution times for all applications                                | 78 |

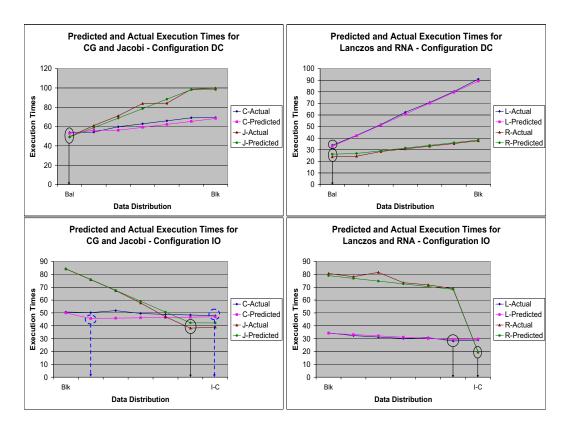

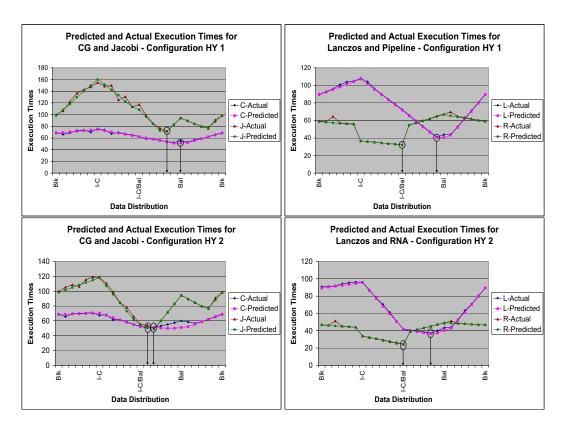

| 6.3         | Actual versus predicted execution times for <i>IO</i> and <i>DC</i> configurations | 79  |

|-------------|------------------------------------------------------------------------------------|-----|

| 6.4         | Actual versus predicted execution times for some architectures                     | 80  |

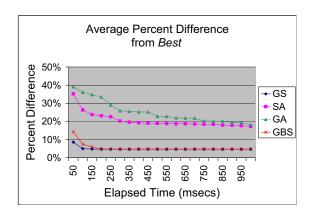

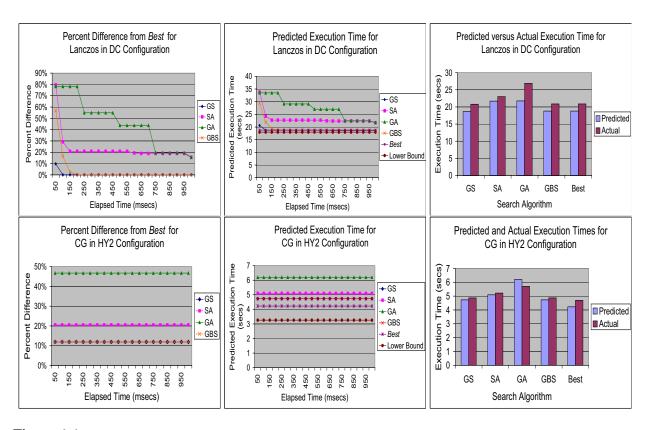

| 6.5         | Percentage difference between GS, GA, SA, and GBS algorithms from Best             | 85  |

| 6.6         | Performance of search heuristics on three architectures running CG                 | 87  |

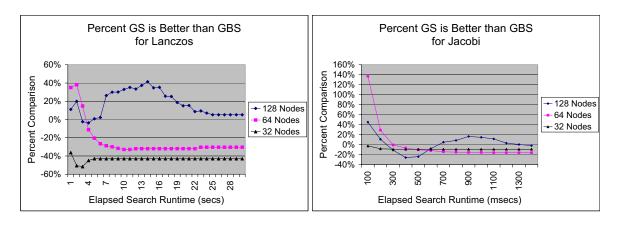

| 6.7         | The scalability performance of the GBS and GS algorithms for Jacobi and Lanczos.   | 88  |

| 7.1         | The composition the complete runtime system, with future work in bold              | 92  |

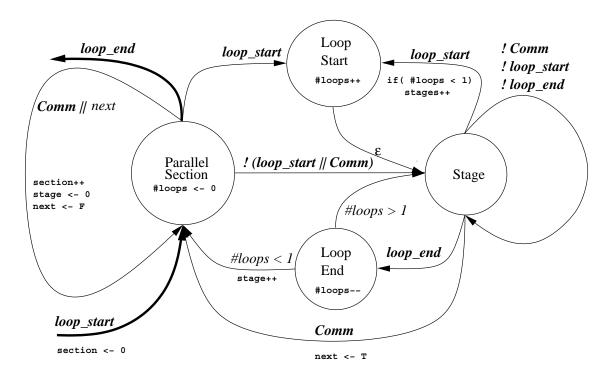

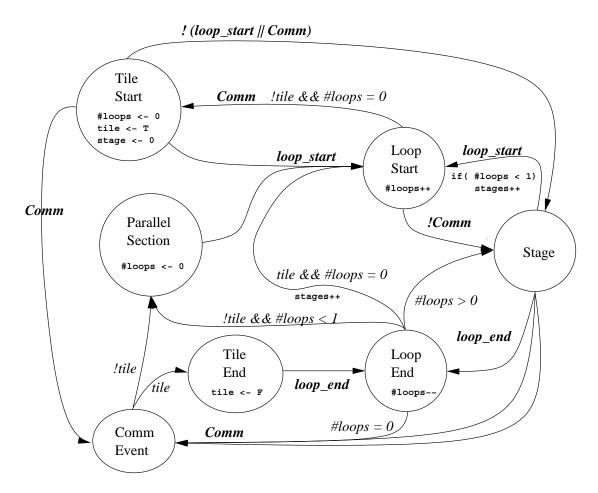

| <b>A</b> .1 | A preprocessor state diagram to break a program into parallel sections and stages  |     |

|             | with nested loops                                                                  | 104 |

| A.2         | A preprocessor state diagram to break a program into parallel sections, tiles, and |     |

|             | stages                                                                             | 105 |

# LIST OF TABLES

| 3.1 | Variables Used in Implementation of the Fitness Function                       | 26 |

|-----|--------------------------------------------------------------------------------|----|

| 3.2 | Common Field values of generated jobs. (Note: STU = Simulated Time Units)      | 33 |

| 3.3 | Results in average turnaround time (ATT) and end times of various task compute |    |

|     | methods (TCM) from baseline tests in STUs                                      | 36 |

| 3.4 | Results in average turnaround time (ATT) and end times of various task compute |    |

|     | methods (TCM) from varying the Critical Number Ranges in STUs                  | 37 |

| 3.5 | Results in average turnaround time (ATT) and end times of various task compute |    |

|     | methods (TCM) from varying the I/O frequencies in STU                          | 39 |

|     |                                                                                |    |

| 6.1 | The configurations of the emulated architectures on which we tested MHETA      | 77 |

| 6.2 | Five emulated architecture configurations used to test search heuristics       | 84 |

#### CHAPTER 1

## Introduction

Computer programs are a popular means to solve problems that involve complicated calculations. Once created and checked for errors, these programs are generally much faster and more accurate than attempting to do the computation manually. This is particularly true in the realm of scientific computing. Scientists describe the inner workings of natural phenomena with complex theories, which they can use to predict the results of experiments. Such theories consist of highly structured and formally written algorithms and are thus relatively easy to encode into computer programs. Without any regard to its efficiency, unfortunately, a naively designed scientific program can run for a very long period of time. One popular technique to significantly reduce a program's completion time is *parallelization*, in which the computational work is divided and spread between many processing units. By having all units work at the same time, they can process parts of the problem simultaneously, and hence the application can finish faster. We calculate the speedup achieved through parallelization as the ratio of the time taken to run the program sequentially over the time taken when run in parallel. Ideally, we would like a perfect linear speedup, which means the execution time decreases proportionally with the number of processors working on the program. (i.e. with P units, the speedup is P, and the application finishes in 1/P of the sequential time).

This ideal is difficult to achieve in general, as there are a variety of problems one must solve to create an efficient parallel application. Some problems are dependent on the structure of the target architecture. At one end of the range is a single multi-processor machine with a single memory that is shared between the processors. Lack of proper synchronization mechanisms in the program can result in race conditions when two processors try to simultaneously manipulate the same variable. Depending on the order in which the data is accessed, the result of the computation can differ,

and the application can produce incorrect output. In addition, upgrading components of this large system is often prohibitively expensive, and some features, such as the number of processors, are difficult to change. At the other end of the spectrum is a *distributed* system, in which each machine in a cluster (individually also referred to as a "node") is a uniprocessor machine with its own memory. Synchronization is typically implemented via message passing, so when two nodes need to access the same variable, they must use explicit communication. Unlike in the multi-processor machine, the amount of aggregate memory scales up as the number of nodes increase. One also can replace, upgrade or add a single machine or component at a time, which is more cost effective than having to upgrade the entire system. These structural characteristics impact how a programmer transforms a sequential program into an equivalent and efficient parallel version. Some of the issues involved to successfully create this parallel version are detailed in Section 1.1.

We assume that the programmer has adequately addressed the problems defined above and has generated the most efficient parallel version of the scientific program. Once the program is ready to execute, two important decisions are (1) the scheduling policy, and (2) the best assignment of the work onto the architecture running the program. Previous work in these last two problems have assumed that the costs to access backup store (the *I/O costs*) are negligible. However, these costs are increasingly difficult to ignore, and this thesis addresses how the I/O costs impact decisions for both when scheduling and distributing work. We started our investigation on the impact of I/O costs on scheduling on a homogeneous cluster. This motivated our change in focus to examine the inclusion of I/O costs when determining an efficient division of work, which will be explored in more detail here. We describe some of the fundamental factors one must consider and the different possible strategies for distributing work in Section 1.2. Section 1.3 presents a general description of the interaction between these issues in more detail, followed by the outline of the dissertation in Section 1.4.

## 1.1 ISSUES IN PARALLELIZING SEQUENTIAL PROGRAMS

The simplest implementation of a program is a consecutive sequence of instructions (in what is referred to the *source code*) to run on a single processor. When parallelizing the program, the programmer rewrites these instructions into an equivalent parallel version in two steps. The user first divides the program into phases and identifies those that can execute in parallel. The programmer then must insert functions to coordinate the execution of the phases to ensure that the output of the application is the same as it would be if it were executed sequentially (i.e. is it *correct*). Some of the issues involved at each of these steps are presented in more detail below.

Some phases, such as those that loop over elements of a multi-dimensional array, are conducive to running in parallel—each processing unit is assigned a subset of the iterations. Other phases can consist of loops with high dependencies between iterations—these cannot efficiently run in parallel and so run sequentially. However, an efficient parallel version may exist for an algorithm that initially seems difficult to parallelize, in which case the programmer could replace the original code with the parallel implementation of the algorithm. Another important issue to address is granularity, a measure of the number and size of the phases. An application that consists of many small phases is generally too fine-grained, which is problematic because the overhead of coordinating them starts to dominate execution time. Therefore, the goal is to make sure the phases will have enough work so that the processing units spend an appreciable amount of time executing them before any coordination occurs.

To ensure correctness, communication or synchronization functions are then inserted at the beginning or end of each phase. The exact mechanism used depends on the target architecture. In a shared memory multi-processor, each processor has access to a shared region of memory. Synchronization is usually implemented using locks or semaphores for access to shared variables, but the programmer still must insert barriers or other control mechanisms to properly prevent race conditions. Our work assumes an alternative architecture, a distributed memory system, where each node has its own memory. Synchronization in this case is usually done via explicit message passing, and

because non-local data must be transferred this mechanism also incurs communication costs. The Message Passing Interface (MPI) library is commonly used to implement communication primitives (sends or receives), and well-defined communication patterns (for example, a reduction or nearest neighbor communication). The programmer can perform this step by hand or rely on parallelizing preprocessors to automatically insert the MPI function calls where necessary. Regardless of how these functions were inserted, we assume applications have been parallelized to run on distributed memory systems using the MPI mechanism for message passing.

## 1.2 DIVIDING THE WORK

In our work, the nature of a distributed memory architecture on which these applications run is assumed to be unknown until just prior to runtime. As the parallel application executes, the runtime system must be able to partition the work so that it runs efficiently. There are two main approaches to solving this problem. The "task parallel" approach assumes there are several distinct phases (called tasks) that can run in parallel, and different ones are assigned to each node. Each node thereby executes a different set of instructions on the data (possibly the same data) and typically communicates after it finishes each task. The important concern in this case is how to order the tasks on the nodes to satisfy their dependency constraints. We address an alternative technique, called "data parallelism", that decomposes the data domain. In these SPMD (Single Program Multiple Data) applications, all the nodes perform the same set of instructions (phase) on the data assigned to them. All nodes run the same phase simultaneously, so there are no ordering constraints to consider as there are in task parallelism. However, all nodes typically participate in a barrier or some other global synchronization function when they reach the end of the phase to share information they need to proceed to the next phase.

Assuming that each node has no memory capacity problems, there are two complications involved with distributing data of SPMD programs. Of lesser importance is that as the data is divided between increasing number of nodes, the time taken to perform computation per node decreases, but the communication overhead increases. The benefits of further parallelizing the

application is offset by the higher communication costs at a certain point. An even more important problem is the large synchronization cost resulting from a poor allocation of data. Taken to an extreme, suppose a single machine is given all the work. The other nodes have essentially no computation, so they reach the synchronization point very quickly. However, the execution time of the program is determined by the completion of the *slowest* node. The completion time of the program itself is slower in this case than if it ran on a single machine because of additional various overheads inherent in parallel execution. A division of data must therefore aim to minimize the maximum of communication and local computation costs of all the nodes simultaneously.

#### 1.3 I/O COSTS AND DATA ASSIGNMENT

Much of previous research on partitioning and allocating data of an SPMD application considers only computation and communication costs. This simplification is possible due to two typical assumptions:

- 1. These applications run on homogeneous clusters in which all nodes have similar characteristics, such as processing power.

- 2. The nodes of the cluster have practically infinite memory capacities.

Indeed, these assumptions are valid for scientific programs running on expensive large scale architectures such as supercomputers with specialized hardware and large memory. However, *heterogeneous* clusters of machines are an increasingly popular alternative due to their cost-effectiveness. They do not rely on expensive hardware, and nodes can easily be added without having to match the configuration of those already on the cluster. A consequence of this shift is that both assumptions are no longer valid. First, the memory sizes of these machines can vary widely, as older machines with smaller memory capacities are networked together with more modern machines with larger capacities. There is now a higher likelihood of a data distribution assigning more data to a node than it can store in memory. Secondly, memory is relatively expensive and small as opposed to secondary storage that is often several orders of magnitude larger and cheaper per byte. Therefore,

large-scale scientific programs, such as those that model weather or analyze satellite images, typically work with very large datasets that can often exceed the total aggregate memory capacity of a cluster. Even adding more machines will not overcome this problem; the accuracy of the application output is constrained by the input data size, and it is always possible to raise the resolution to get better results.

Given a data distribution in this computing environment, a node that cannot store the local portion of the working data in memory must save it on disk (sometimes referred as the backup store). The application is then *out-of-core*, and the local dataset must be read from and written to disk in pieces. Hardware optimizations such as write-back buffers allow a call to the write function to return quickly, reducing the effective latency of that operation. Reading data from the backup store is in contrast potentially very expensive because the application must wait for the data to arrive from disk before it can proceed. Ignoring either cost usually results in poor performance, as the speed of memory and processors continue to out-pace the progress of I/O latency reduction. This large disparity is due to the fact that reading data from a magnetic disk involves mechanical operations (movement of the reading arm and the platters in which the data is stored) which are orders of magnitude slower than accessing memory. For this dissertation, a local, single disk drive is assumed, but the backup store can be on a disk of a remote machine; the latency has the potential to be even larger if one adds costs to transfer the data over a network. Our target scientific applications repeat computation over several iterations, and the entire local dataset must be read from and potentially written to disk at each iteration, multiplying the I/O costs.

The consideration of I/O in data distributions introduces an additional trade-off. Data distributions that minimize accesses to disk and avoid expensive latency costs are desirable. As the same time, the computational power of the nodes in a heterogeneous cluster are non-uniform, requiring a data distribution that also minimizes load imbalances. Any benefit from assigning more data to a node with a faster CPU and small memory in order to balance the workload can be offset by the penalty of accessing the disk, resulting in overall poor performance. This penalty is exaggerated if the access speed of the disk is also very slow. We therefore extend the problem of distributing

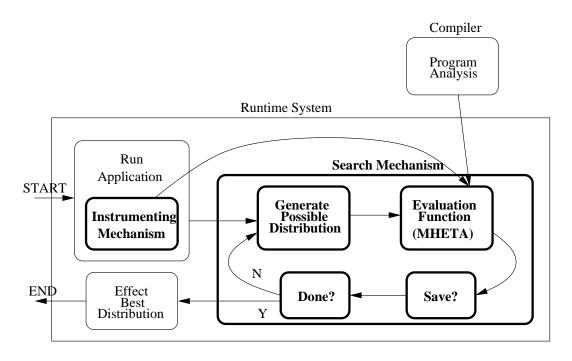

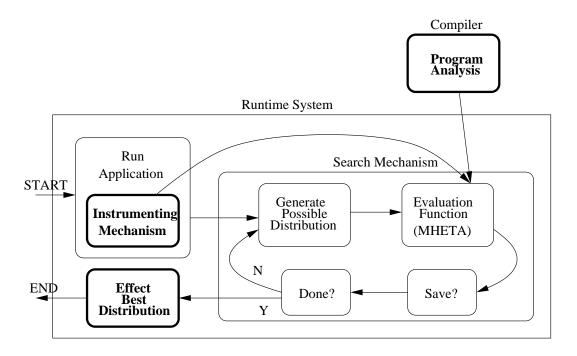

Figure 1.1: The general structure of the SHARED runtime system. Two components, the search mechanism and the MHETA evaluation function, have already been implemented and are detailed in Chapters 4 and 5, respectively. The instrumenting component is partially done by hand, and details for automating both this process and program analysis by the pre-processor are described in Chapter 5.

data to minimize the maximum execution time of an out-of-core application running on a heterogeneous cluster. This time includes the costs to perform computation, communication, *and* disk accesses of all the nodes; this is the *out-of-core heterogeneous data distribution problem*.

Our eventual goal is to develop a runtime system we call SHARED (System for Heterogeneous ARchitecture Efficient Data distributions) shown in Figure 1.1 that automatically determines the best distribution of data for large-scale scientific applications. Two main portions of this system, the data distribution search mechanism and its evaluation function, have already been implemented. We first note that an exhaustive search through all possible data distribution candidates is computationally intractable. Therefore, we developed a guided search heuristic we call *GBS* (Generalized Binary Search) that starts from a random candidate which it then continually modifies until no more improvement is possible. The *GBS* algorithm is based on the assumption that there is a monotonic

relationship between how much data and work are assigned to a node with the length of time it will take to finish the work. We prove that this algorithm is optimal under these circumstances. Secondly, we developed a computational model for parallel execution called MHETA (Model for HET erogeneous Architectures) that takes as input a data distribution and outputs a predicted execution time of the program. MHETA is used to evaluate distributions by both the GBS algorithm as well as others we used to compare its performance. This model incorporates information about the runtime environment, architecture properties, and application structure, ensuring its accuracy at runtime. These two components enable our system to determine an effective data distribution on the fly.

We determined through testing that MHETA is on average at least 97% accurate in predicting the execution times of four applications running on a variety of emulated architectures. This indicates that distributions found by search algorithms using MHETA (*GBS* included) are valid. Further, we show that our *GBS* algorithm outperforms other heuristics and is within 5% of the best distribution we found<sup>1</sup>. It does not scale initially as well as a greedy search algorithm, but as the number of nodes increases further, *GBS* outperforms the greedy search, which often becomes stuck at a local optimum.

#### 1.4 DISSERTATION STRUCTURE

This thesis is structured as follows. Chapter 2 details related research. We introduce a summary of various important issues when scheduling parallel programs and the important of I/O awareness in these schedulers in Chapter 3. Chapter 4 continues with analysis of the proposed MPI-based runtime system to automatically solve the data distribution problem for heterogeneous architecture. Chapter 5 describes the computational model used by this system, followed by performance results for both these components in Chapter 6. We will conclude and describe some future directions in Chapter 7.

<sup>&</sup>lt;sup>1</sup>The method by which we establish the best distribution used for comparison is detailed in Chapter 6

## CHAPTER 2

## RELATED WORK

A significant amount of research has been done that is related to the work described in this dissertation. We divide it into four broad categories: modeling, data distribution, out-of-core parallel programming, and non-dedicated and heterogeneous computing. This section discusses each of these in turn and compares them to our work.

#### 2.1 Modeling

Many of the research areas in modeling applications are summarized in a survey by [36]. One area is concerned with modeling communication, either through shared memory or explicit message passing. Another related area is in modeling the transfer of data through the memory hierarchy—from cache to main memory to disk. These models are used to either (1) establish theoretical time or space complexities, or to (2) produce performance metrics that enable researchers to compare implementations of various parallel algorithms. Therefore, they often aid in the design of efficient algorithms or prove their optimality.

## 2.1.1 Modeling Communication

The Block Distributed Memory (BDM) [29] model, Bulk Synchronous Parallel (BSP) [55] model and LogP [16] are three examples primarily used as a framework for designing and analyzing algorithms. The BDM model takes as input the number of processors, the message size, the maximum communication latency, and the rate a processor can inject a word onto the network. Using these inputs, the authors aim to develop algorithms that maximize computation speedup while simultaneously minimizing communication costs. The BSP model uses *supersteps*, primarily consisting

of computation (and possibly I/O) and limited communication. Once a node reaches the end of the superstep after a uniform computation duration, it synchronizes with every other node. Programmers can use this model in designing algorithms, determining when to replicate versus distribute data, and deciding the optimal hardware configuration for communication. LogP models parallel programs using latency, overhead, gap, and number of processors. The computation in this model is simplified and assumed to take unit time, but LogP does consider the fact that the network has finite capacity (bandwidth). LogP was designed as a basis to develop fast, portable parallel algorithms.

Two of these models, LogP and BSP, have variants that address some of their shortcomings. LogGP [4] is an extension of LogP that was developed to more realistically calculate the overhead of long messages, which is typically subdivided and sent in pieces. Whereas LogP adds overhead to sending each piece, LogGP adds only a *single* overhead cost. Another parameter, G, is the amount of time needed to load that part of the message into the network; thus, the communication cost is the overhead plus G times the number of pieces in the message. The authors used LogGP to design and analyze algorithms, such as all-to-all remap, FFT, and radix sort. Memory logP [11] is another extension of LogP to include memory to memory communication through a distributed shared memory buffer, and it is used to predict and analyze the latency of memory copy, pack and unpack operations. Heterogeneous BSP (HBSP) [60], a variation of the BSP model, will be discussed in more detail in Section 2.4.

## 2.1.2 Modeling the Memory Hierarchy

Vitter and Shriver [57] developed a realistic parallel block transfer model in which a contiguous block of data is retrieved from multiple disks simultaneously. They used their model to try designing sorting algorithms that minimize the number of disk accesses they require. The Hierarchical Memory Model(HMM) [2] was used to investigate the theoretical complexity of solving problems in a machine with a memory hierarchy, particularly with exploiting locality of reference. One area of their investigation is the Least Recently Used (LRU) replacement strategy based on recent memory access patterns (on-line LRU), which moves data from smaller but expensive

memory to cheaper but much larger memory. The authors used HMM to show that on-line LRU is as effective in maintaining spatial and temporal locality across levels of the memory hierarchy as the best algorithm designed using trace information.

The Parallel Memory Hierarchy (PMH) model [5] is a generic model of parallel computation that extends the memory hierarchy to multiple machines. The architecture is represented as a tree where each vertex represents a component, such as a network component or a machine's memory or disk, and the leaves represent processors. The edges are the transfer paths of data from one component to another. The PMH model includes equations for each edge to calculate latency costs and also considers contention when data from many components must share resources. They provide an algorithm to design the tree most suited to the architecture, which can be combined with measurements of specific behaviors to create an accurate model.

#### 2.1.3 COMPARISON WITH OUR APPROACH

Our use of MHETA is orthogonal to the goals of models like LogP. We assume that the programmer designed the best possible implementation of the parallel application, possibly by using these models described above. MHETA can then be used to determine an efficient data distribution for parallel applications during runtime. We require accurate measures of the costs to perform computation, communication and I/O for MHETA, which involve measuring these components during an instrumented run. The main focus of the distributed models is in the design of more efficient communication, thus many models make simplifications of the computation involved. The PMH model is the closest to the modeling approach we use, but unlike MHETA, it does not predict execution times, and particular architectures, such as 2-dimensional meshes, cannot be accurately modeled.

## 2.2 DATA DISTRIBUTION

There have been three primary approaches to data distribution: language annotations, compiler analysis, and run-time adaptation. We discuss them in turn.

One way to distribute data is to provide language annotations and allow the programmer to choose the distribution using application-specific knowledge. This is the approach taken by HPF [25], which was motivated by many others' work (e.g., [26]). In this approach, the programmer annotates each array, stating whether it is distributed, its alignment, and its distribution pattern. Compiler techniques to distribute (and possibly redistribute) data have also been studied extensively (e.g., [6, 24, 45, 31, 43]). The basic idea behind compiler-based systems is to analyze the source code to determine the communication pattern and then choose a BLOCK- or CYCLIC-based distribution that balances the load. Approaches employing a run-time system, such as CHAOS [28], AppLeS [7], SUIF-Adapt [38], and CRAUL [46] can use run-time information to find an efficient data distribution. This is especially effective in cases where workload and communication characteristics of a program change at run time.

#### 2.2.1 COMPARISON WITH OUR APPROACH

The work described above addresses the data distribution problem, not the heterogeneous data distribution problem; the latter problem allows processor speed, memory size, and I/O speed to all differ. This requires a trade-off between balancing load, minimizing communication, *and* minimizing I/O. Further, systems like AppLeS always avoid using a processor if its memory is relatively small, even if that processor could perform useful work.

#### 2.3 Out-of-core Parallel Programming

Many researchers have studied out-of-core parallel applications, where data structures must primarily reside on disk. A programmer can write these applications just as in-core ones, using the virtual memory system with demand paging for all I/O. This approach has the advantage that the user is not required to restructure an in-core application, but it is usually inefficient because the operating system has only local information about memory access behavior. Therefore, (1) disk reads typically incur full latency and (2) the page replacement strategy can often be suboptimal for certain classes of applications. Users could alternatively manage I/O directly by inserting explicit

read and write calls in their applications. Although the programmer can design file accesses with program specific patterns in mind, the restructuring of an application is error prone. Even in perfectly transformed code, disk reads still typically incur full latency, and the transfer units could be small, such as when columns are read from a matrix stored in row-major format.

Asynchronous I/O is a technique that can dramatically reduce the experienced latency of disk reads, and progress of this area is discussed in Section 2.3.1. Collective I/O techniques (in Section 2.3.2) aim to combine a series of small requests into a single large one to be handled efficiently by the file system, ensuring large transfer units and also reducing latencies. User defined virtual memory management, discussed in Section 2.3.3, allow the user to manage the virtual memory to accommodate their application's accesses patterns. Finally, work in generating efficient out-of-core applications through a combination of compiler and runtime techniques is discussed in the last section.

## 2.3.1 ASYNCHRONOUS I/O

One extensively studied technique to hide disk read latency is prefetching. The basic idea is to separate when a disk read is issued from when the data is actually accessed. Ideally, the latency can be completely masked with overlapping computation by issuing the prefetches early enough. Issuing prefetch calls too early, however, can result in unnecessary movement of data to and from backup store as both (1) requested and (2) currently used data try to occupy memory simultaneously. This situation is difficult for out-of-core applications because the datasets currently being processed typically take up all of memory. Therefore, the system issuing prefetches needs information about an application's future access patterns, which can be determined either through compiler analysis, past behavior, or speculative execution. Mowry et al. [39] use a memory model during static analysis to establish locality of accessed variables to insert non-binding prefetches and releases when compiling an application. Agrawal et al. [3] designed a compiler that takes programs written in Fortran-D and replaces explicit regular I/O calls with their asynchronous counterparts, even across procedure boundaries. Others monitor access patterns in the operating system and use the results

to prefetch data [33, 22, 61]. In [13], the authors use speculative execution while an application is blocked waiting for data to arrive from a file read to generate hints for more effective future prefetching. Finally, in [44], applications advise the OS of their future access patterns.

## 2.3.2 Collective I/O

The server-directed I/O [47] and active buffering [35] in Panda, disk-directed I/O(DDIO) [32], and two-phased I/O in PASSION [10, 53], are three areas of work on *collective I/O*. All these areas of research are on distributed systems divided into two set of nodes. One set of nodes perform primarily computation, and the other set manage I/O. These two sets are called clients and servers in Panda and compute processors (CP) and I/O processors (IOP) in research in DDIO and PASSION. Any data that clients cannot store in local memory must be stored on disks on the servers. The layout of the data on the servers disks can differ greatly from its distribution onto the clients, so a client can have its required data stored in small non-contiguous pieces scattered onto many servers. The client thus will send many small I/O requests for data that is actually accessed in a regular pattern, often called the *stride*. Servers generally cannot perform any optimizations because they only have local information about how data is accessed—high-level semantic information describing the stride of reads or writes is lost. Therefore, servers tend to perform many small I/O operations for data that can actually be done with a single large operation. The basic idea of collective I/O is to introduce high-level interfaces by which this semantic information can be sent to the servers to allow it to retrieve and write data efficiently.

In the Panda library, a single client and server pair is selected as the coordinators of a collective I/O event. This client collects the read requests from the other clients into a schema detailing the local layout of the data to client memories. It then sends these schemas to the coordinating server, which shares this information to the other servers holding the pieces of data on their disks (called subchunks). For read requests, each server efficiently retrieves all the data and then sends each subchunk to the client that requires it.

In DDIO, each IOP collects read/write requests from the CPs during collective communication and determines the most efficient means to retrieve data from disk. The node responsible for the data can (1) collect several requests of data from the same disk, (2) efficiently read this single request and (3) send the results to the respective nodes. This indirection technique is most effective when the requested data is in a regular but non-sequential pattern from within the compute node and closely located items are located in different I/O nodes. This transformation also helps when the in-memory data has a different layout than on-disk data. One example occurs when a CYCLIC distribution is used in memory but a BLOCK distribution is used on disk.

## 2.3.3 USER-MANAGED VIRTUAL MEMORY

Research in [12] and [15] focus on the fact that the popular Least Recently Used (LRU) page replacement strategy is inadequate for a class of scientific applications with access patterns such as streaming. A tool combining the MMUM (Memory Management in User Mode) library and the MMUSSEL (Memory Management in USer SpacE Level) modules was created so the user can define his own strategy that suits the application. An alternative is to use the Transparent Parallel I/O Environment (TPIE) [56], which also hides the details of the I/O subsystem from the user. It consists of a templated library to provide efficient, high-level coordination of data movement between disk and memory. It uses the parallel block transfer model described in Section 2.1.2 in order to determine the best algorithm to move the data.

#### 2.3.4 COMPILER AND RUNTIME ANALYSIS

Compiling out-of-core codes is described in, for example, [52, 9]. One basic idea of this work is to extend the data parallel model to out-of-core programs. Another key idea is tiling, an optimization previously used to rewrite loops to keep data in cache as long as possible. One run-time approach, called SMARTS, schedules work dynamically to help reduce disk accesses [54]. This system employs a dataflow model to determine dependencies between various tasks to schedule work when all of their predecessors have completed. By scheduling in a LIFO manner, data in the

cache produced by a predecessor is likely to still remain when accessed again. Although the focus of SMARTS was on the cache, the technique could also help out-of-core programs in which the data being read is not streamed through.

## 2.3.5 Comparison with Our Approach

Our work is orthogonal to techniques to improve out-of-core parallel programming. We start from an efficient user program, which can be by hand or by the above techniques. We then seek a data distribution that could potentially eliminate I/O altogether while balancing the load as much as possible.

#### 2.4 Non-dedicated and Heterogeneous Computing

Several researchers have studied various parallel computing problems on non-dedicated or heterogeneous clusters. Gang scheduling is a technique in which multiple parallel jobs execute concurrently in a non-dedicated environment, but a subset of the processors is given exclusively to a single job at a time. Extensive research has investigated the benefits of gang versus other scheduling algorithms, such as variable and dynamic partitioning [50]. The flexibility provided by the gang scheduler makes it a competitive scheduling strategy [17]. In fact, the Lawrence Livermore National Laboratory have deployed gang scheduling onto several of its computing platforms with high success [30]. A major challenge is to determine which applications should be gang scheduled. Both message passing characteristics [49] and use of shared communication objects [19] were used to detect gang candidacy. Nikolopoulos et al. [42] also manage the trade-off between paging and gang scheduling on a multiprogrammed cluster.

There has also been work on compile and runtime libraries for running parallel applications on heterogeneous clusters. The MPI [40] and PVM [51] libraries support message passing between *different* architectures. To function on diverse architectures, such libraries must make sure, for example, to handle potentially different byte orderings. Grid MPI is an extension of MPI that

enables an MPI written program to use grid services [21]. There has also been work done in compiling for heterogeneous machines [59]. This involves, for example, developing an intermediate form that permits arbitrary orderings of transformations. Finally, the HBSP model mentioned in Section 2.1.1 calculates the duration to perform computation between nodes with differing computational powers. The superstep duration is then calculated as the computation time taken by the slowest node, the slowest communication between pairs of nodes, and the communication overhead. This model can aid the user in designing an efficient parallel application that is compiled and run on a heterogeneous cluster.

## 2.4.1 Comparison with Our Approach

Gang scheduling is expensive to implement and is most often implemented on supercomputers. Also, [42] involves modifying the OS. Our work is focused on the runtime system on clusters, where gang scheduling is unlikely to be present. Message-passing libraries are complementary to our work, and the HBSP model does not consider the impact of I/O as MHETA does.

## CHAPTER 3

#### I/O-AWARENESS IN GANG SCHEDULING

We first investigate the benefit of including I/O costs in scheduling distributed applications. Scientific applications running on a multiprogrammed environment often compete with other programs for resources, such as time on the CPU and memory space. Schedulers for sequential programs running on a single uni-processor machine primarily ensure that each program is allotted an equal number of time slices (a period of time to execute on the CPU). Strategies such as round robin are designed so that both large and small applications (jobs) get an opportunity to run and do not starve; this policy increases throughput as smaller jobs finish faster. A distributed application is divided into many pieces of executing instructions (processes) that run on multiple machines (nodes) and often need to communicate with each other during their execution. Therefore, schedulers for these jobs must also be able to coordinate how each process runs on its machine in the underlying architecture. Gang or co-scheduling is one such strategy, which groups the processes of an application into a gang and schedules them to run simultaneously. In doing so, it can increase the likelihood that the recipient and sender of messages at a communication point are executing at the same time, potentially greatly reducing the time a receiver of a message has to wait for the message to arrive. An effective scheduling strategy is thus vitally important to minimize a large scale scientific application's execution time.

An important input for gang schedulers is how many nodes onto which to schedule a job. One approach is to assume the job is broken into many processes and run the job on all the nodes. Unfortunately, communication costs do not scale, and the speedup for data-parallel programs eventually tails off as the number of nodes it uses increases beyond a certain point [48]. Applications with a low degree of parallelism are particularly unable to efficiently utilize large number of the additional

nodes given to them. When there are too few nodes, on the other hand, the data local to a node can exceed its memory capacity, introducing I/O costs, which also adversely affects execution times. In either case, a job will take longer to finish and use resources that could have been allocated to another job, thereby increasing the completion time of both jobs.

The delay as a result of introducing I/O latencies is an order of magnitude greater than from increasing communication costs. Therefore, there is a great benefit to scheduling a job on the minimal number of nodes required to ensure that its dataset is in core (called the critical number or CN). Note that we are concerned with scheduling and not finding an efficient distribution of data. Data distribution is discussed in Chapters 4—6. Here, we assume that the job's data is divided into CN equal pieces. The scheduler can assign the processes to CN nodes and eliminate I/O while leaving nodes open for other programs to be scheduled, increasing throughput. We determined through simulation that using an application's CN would speed up its execution time by as much as a factor of three when compared to gang-schedulers that assigned all the nodes to an application. When we further modified the gang scheduler to schedule applications with smaller CN more frequently, we see an even greater throughput and reduced time to completion because more applications finished faster. I/O-awareness via a job's CN is therefore useful to bring jobs in core when possible and use the processors they were assigned most efficiently.

Section 3.1 will present a brief overview of gang scheduling, followed by details on the simulator used in Section 3.2. The last section will present results to show that the question of impact of I/O is worthy of pursuit.

## 3.1 GANG SCHEDULING OVERVIEW

Gang scheduling is an algorithm that groups all processes of a data parallel program into a gang and schedules them to run on the architecture simultaneously. Therefore, the user is presented with the illusion of a dedicated environment, and the sender and recipient processes are more likely to be executing when they reach a communication point. We assume that all these programs (*jobs*) are gang scheduled. The first subsection will describe the features of the gang scheduler used in the

simulator. This is followed by special properties of gang schedulers that reduce the effectiveness of asynchronous I/O techniques.

#### 3.1.1 THE GANG SCHEDULER INTERFACE

The gang scheduler interface in the simulator we designed uses a two dimensional array called a trace matrix. Although other control structures, such as the Directed Hierarchical Control (DHC)[18] have been investigated, the matrix approach was selected for its relative simplicity in implementation. Each row corresponds to a time slice, and each column represents a processor. An entry in location (i, j) contains the ID of the process to run on processor  $P_j$  when the scheduler is pointing to row  $R_i$ . When that time slice expires at a "global time slice event", the scheduler preempts and suspends all the processes running in  $R_i$  and schedules the processes in the entries located in row  $R_{i+1}$ . There is overhead in a real system during this event when coordinating all the processors, but the simulator does not measure this cost. The time slice duration is usually large enough so that the effect of this overhead is lessened.

At any time, some rows are empty, while others contain one or more non-empty entries and are considered valid. A "period" refers to the number of valid rows in the matrix. The rows are processed round robin, and when the last valid row is reached, the scheduler returns to  $R_0$ . Jobs with a predetermined number of processors are scheduled into the matrix in the first row that can accommodate them. As the active jobs increase in number and occupy more rows in the matrix, the size of the matrix also increases, and more time will elapse between successive time slices for each job. Formerly valid rows may become empty as jobs finish, so the matrix is compacted at every global time slice event to remove non-valid rows. For simplicity, the time slice duration is kept constant for all the rows in the matrix.

## 3.1.2 Unique Implications of Ignoring I/O in Gang Schedulers

Gang scheduled processes cannot hide I/O latencies when accessing the disk because context switches are not allowed in the middle of a time slice. CPU fragmentation [34] can result as the

processors running the processes are forced to remain idle. Additionally, all processes are preempted when switching from one row of the trace matrix to the next, so prefetching is difficult to use. It is not possible in the general case to determine in advance if the process that issues such a request is still running when the data arrives. If in fact a different process is scheduled on the node instead, both the prefetched data from the previous process and data swapped in from disk for the current process are now loaded into memory at the same time, resulting in thrashing.

The fact that I/O latency cannot be effectively masked in general reduces the amount of progress jobs can achieve even when gang scheduling is used. The sender of a message during a communication event may be performing I/O, so the recipients of the message must contend with both the latency of the communication as well as the I/O of the sender. They will stay blocked until the sender finishes its I/O and they receive the message. In the worst case, the time slice for these processes may expire, and the sender will then only be able to send the message the next time it is scheduled. This compounded latency experienced by this job will result with it staying in the system longer and occupying rows in the trace matrix that could otherwise have been used by another job. This situation increases the turnaround time of the other jobs.

## 3.2 Implementation

We created an I/O-aware gang scheduling simulator by modifying the Schark simulator [8], described in Section 3.2.1. Extensions to the job description facility are described in Section 3.2.2. The primary modifications we made are encapsulated in several modules, which will be described in the last three subsections.

# 3.2.1 THE ORIGINAL SIMULATOR

The Schark simulator is written in Java and simulates the behavior of several jobs running on a specified system. The model of computation used is probabilistic, so every feature of a job, such as execution time and number and frequency of I/O events, are based on random distributions defined

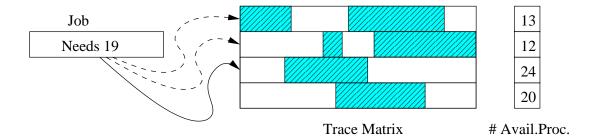

Figure 3.1: Picture of how a job is inserted into the trace matrix. The non-shaded regions of each row are unused. The job requests 19 processors, and there are 13, 12, 24, and 20 processors available in the rows of the trace matrix. The job is placed in the first row that has enough processors. In this case, it is the third row.

in a job description file. Supported distributions include uniform, hyper-Erlang, and normal. Multiple job types are allowed, and a mixture is generated when the simulator starts. The jobs are described in a *job description file*, which contains such information as I/O frequency and duration, communication frequency, initial number of processes and the time they end. It supports several kinds of interconnection networks, such as tori and meshes, the descriptions of which are included in a separate description file. Schark uses a simple gang scheduler interface and uses bin packing to schedule jobs into the trace matrix. The process IDs of a job are inserted into the first available row in the trace matrix, as shown in Figure 3.1.

## 3.2.2 Job Description Extensions

The introduction of I/O costs in gang scheduled jobs motivated four additions to the job description for  $J_i$ . They are: the critical number  $(CN_i)$ , total sequential computation time  $(T_s^i)$ , the number of iterations involved in the computation  $(N_i^{iters})$  and the percent of its computation that can be performed in parallel  $(P_i)$ . Given  $N_i^p$ , the initial number of processors allocated to the job, we can calculate the total time  $J_i$  spends working via the standard weighted average formula:

Total Computation (work) =

$$\left( \frac{(100 - P_i) + (P_i/N_i^p)}{100\%} \right) * T_s^i$$

(3.1)

Unlike the original Schark simulator that assigned a random end time for a job, the end time now occurs when its remaining computation time is reduced to zero.

We calculate the total number of I/O events that process produces  $(N_i^{IO})$  as a function of  $N_i^p$ ,  $CN_i$  and  $N_i^{iters}$ :

$$N_i^{IO} = \begin{cases} 1 & \text{if } N_i^p \ge CN_i \\ \left\lceil \frac{CN_i \cdot N_i^{iters}}{N_i^p} \right\rceil & \text{otherwise} \end{cases}$$

(3.2)

If  $N_i^p \geq CN_i$ , then the process performs only one I/O event, which is to initially bring in its working set. Otherwise, we assume that the sequential job issues I/O events  $CN_i$  times during a single iteration. The total number of I/O events is thus  $CN_i \cdot N_i^{iters}$ , and the parallel version is assumed to divide the I/O evenly amongst its  $N_i^p$  processors. The total number of I/O events is inversely proportional to  $N_i^p$ , so as  $N_i^p$  increases, the number of I/O events drops until it reaches one (when  $N_i^p = CN_i$ ).

The time between I/O events  $T_{IO\leftrightarrow IO}^i$  is calculated as the total sequential execution time divided by the total number of I/O events issued in the sequential program:

$$T_{IO \leftrightarrow IO}^{i} = \frac{T_{s}^{i}}{CN_{i} \cdot N_{i}^{iters}}$$

(3.3)

Finally, nearest neighbor, scatter and gather communication patterns were implemented to model three types of communication typically exhibited by distributed programs.

## 3.2.3 ALGORITHM OVERVIEW

Given  $J_i$ , the bin-packing assignment used by the original Schark simulator is simple and efficient. However, it may result in poor turnaround time and throughput in the case  $N_i^p < CN_i$  as processes start to incur I/O costs. Our goal is to design a polynomial-time algorithm that runs small jobs more often in the trace matrix, while also attempting to satisfy I/O needs of a job to keep it in core. By assigning  $J_i$  more rows in the trace matrix when its critical number is less than the number of processors in the system  $(CN_i < N_S^p)$ , it has more opportunities to run per iteration through the trace matrix. Smaller jobs therefore finish faster, potentially condensing the trace matrix as rows become empty, resulting in lower average turnaround time for every job in the system.

At a high level, the algorithm finds  $N_i^s$  rows in the trace matrix to place  $J_i$ . If the critical number for  $J_i$  is greater than  $N_S^p$ , it assigns  $J_i$  onto one row. Otherwise,  $N_i^s$  is calculated as the ratio of  $N_S^p$  and  $CN_i$ .

$$N_i^s = \begin{cases} \lceil N_S^p / C N_i \rceil & \text{if } C N_i \le N_S^p \\ 1 & \text{otherwise} \end{cases}$$

(3.4)

Accordingly, we assign  $J_i$  its critical number of processors unless that exceeds  $N_S^p$ :

$$N_i^p = \begin{cases} CN_i & \text{if } CN_i \le N_S^p \\ N_S^p & \text{otherwise} \end{cases}$$

(3.5)

It then finds  $N_i^s$  rows in the trace matrix that can accommodate  $J_i$ .

We also take into account not only the entering job, but all the other jobs in the system. The next section describes our algorithm in detail.

## 3.2.4 ALGORITHM DETAILS

This section formalizes the algorithm used to schedule jobs and is split into two portions. The first focuses on the fitness of row and processor assignments of job  $J_i$  in isolation, and the second calculates the overall fitness of all the jobs. Those with lower fitness spend less time performing computation, so their progress is slowed. Our ultimate goal is to select a configuration for  $J_i$  that results in the most system-wide progress to job completion. Although the description included here is based on the features of a particular job, the times are actually measured at the level of its processes. Once these numbers are known, they are integrated to model the execution behavior of the job itself.

We first define our assumptions, followed by a description of several additional variables we use in this function. The third subsection describes the function, and we conclude with the time complexity analysis to compute the entire fitness function.

## ASSUMPTIONS AND VARIABLE DEFINITIONS

We make a few assumptions to simplify the design of the fitness function. First,  $N_i^p$  and  $N_i^s$  are write-once variables. If they are allowed to change, extensive detection is required. Our algorithm is designed to schedule  $J_i$  into multiple rows of the trace matrix, and there is no guarantee that a particular process will be assigned to the same processor for each row. Therefore, a process will likely need to migrate (i.e. move from one processor in one row to another processor in another row). By assuming the architecture is homogeneous, the cost for migration can be calculated in the same manner regardless of the direction of movement. Finally, communication costs are not factored into the fitness function (but are in job execution), as they complicate the model but are often dominated by I/O latency in out-of-core parallel programs.

There are several variables that need to be defined for this function, and they will also be used in the remainder of the chapter. Four variables deal with times spent performing I/O, context switches and migration. The value in  $T_w^{\beta}$  is the amount of time required to load the next required data elements from disk during a single explicit I/O event. This value is a function of the size of the data accessed. The variable  $T_w^i$  denotes the total amount of time job  $J_i$  spends loading the working set during one trace matrix iteration. Variables  $T_c^i$  denotes the total context switch time, and  $T_m^j$  denotes the total migration time between different processors for  $J_i$  on one trace matrix iteration. A fifth variable,  $T_s^i$ , stores the duration of a time slice in the system.

There are five other variables to store various values of some of the characteristics of the system or of  $J_i$ . Three variables,  $N_S^p$ ,  $N_i^p$ ,  $N_i^s$  and have already been defined. The variable  $N_M^r$  is the number of rows in the trace matrix after  $J_i$  is inserted. Finally,  $N_i^{IO}$  stores the number of I/O requests performed by  $J_i$  per time slice. This value can be calculated by multiplying the I/O frequency by  $T^s$ . For k jobs, there have to be k copies of each of these three variables. Table 3.1 summarizes these variables.

| Name          | Description                                                                           |

|---------------|---------------------------------------------------------------------------------------|

| $T_w^{\beta}$ | amount of time required to load the required data from disk during an                 |

|               | explicit I/O event.                                                                   |

| $T_w^i$       | total amount of time per iteration of the trace matrix $J_i$ spends performing        |

|               | explicit I/O                                                                          |

| $T_c^i$       | total amount of time per iteration of the trace matrix $J_i$ spends in a              |

|               | context switch.                                                                       |

| $T_m^i$       | total time that $J_i$ spends migrating during a single iteration through the          |

|               | trace matrix.                                                                         |

| $T^s$         | duration of a time slice in the system.                                               |

| $N_S^p$       | total number of processors in the system.                                             |

| $N_i^p$       | number of processors alloted to this job.                                             |

| $N_i^s$       | number of time slices for $J_i$ .                                                     |

| $N_M^r$       | number of rows used in the trace matrix after the last job, $J_{last}$ , is inserted. |

| $N_i^{IO}$    | number of I/O requests performed by this job per time slice.                          |

Table 3.1: Variables Used in Implementation of the Fitness Function

## PROGRESS MEASUREMENT

The optimum progress a job  $J_i$  can make towards completion during a single iteration through the trace matrix is:

$$T_o^i = (N_i^s * T^s)$$

The actual progress is limited by time spent performing I/O, time spent context switching, and time spent in migration. The last two factors are the result of assigning  $J_i$  to multiple rows, and our fitness function must include these. The first and most significant factor is  $T_w^i$ , the total amount of time required to move data between disk and memory during a single iteration, which increases with the number of disk accesses. This makes it vital to keep a job in core, if possible. In our model, we assume that the processes of a job all have the same number of I/O requests. Hence,  $T_w^i$  is equal to the product of (1) the number of I/O requests issued during a time slice, (2) the number

of time slices allocated to  $J_i$ , and (3) the duration to retrieve the data:

$$T_w^i = N_i^{IO} \cdot N_i^s \cdot T_w^\beta$$

The second factor is the cost associated with context switching the processes of  $J_i$  when its current time slice starts. When necessary, it consists of the duration to restore the state of a process as well as loading its working set from swap. Suppose  $J_i$  is assigned to only two rows in the trace matrix ( $R_a$  and  $R_{a'}$ ). A process scheduled on the  $j^{th}$  processor has no context switch costs if it is the only one running on that processor between  $R_a$  and  $R_{a'}$ . Otherwise, the process incurs overhead to restore its state and load its working set that had been swapped out when a process of a different job ran on that processor. We calculate  $T_c^i$  as the average of all context switch costs incurred by all of its processes during a single iteration through the trace matrix.

The third factor to reduce  $T_o^i$  is the cost, if any, for the processes of  $J_i$  to migrate between processors. This only occurs when a process runs on one processor in row  $R_a$  and a different one in  $R_{a'}$ . If the processes stay on the same processors, this duration is reduced to zero. The value of  $T_m^i$  is also the average migration time over all of the processes in  $J_i$  during one iteration in the trace matrix.

The total amount of progress  $J_i$  makes towards completion during one iteration through the trace matrix is the optimum minus the three factors discussed above (time spent accessing the disk, context switching, and migrating):

$$T_o^i = T_o^i - (T_c^i + T_m^i + T_w^i)$$

Intuitively, the relative progress of any job in the trace matrix depends on  $N_M^r$ , which may increase as a result of adding one or more rows to the end in order to fit  $J_i$ . We can calculate the total amount of relative progress of all the jobs during one iteration of the trace matrix  $(T_\rho^C)$  as the sum of the relative progress of all the jobs.

$$T_{\rho}^C = \frac{1}{N_M^r} \cdot \sum_{i=0}^k T_{\rho}^i$$

### TIME COMPLEXITY OF FITNESS FUNCTION

For each job  $J_i$  the time complexities to evaluate the time all k jobs spend during explicit I/O, context switch and migration are O(1),  $O(N_M^r \cdot N_i^p \cdot N_i^s)$  and  $O(N_i^s \cdot N_i^p)$  respectively. It is clear that  $(\max_{i=0...k} N_i^s) \leq N_M^r$ , so the time complexity to perform the fitness function  $(T_f)$  for all k jobs is

$$T_{f} = O\left(\sum_{i=1}^{k} \max\left\{O\left(1\right) + O\left(N_{M}^{r} \cdot N_{i}^{p} \cdot N_{i}^{s}\right) + O\left(N_{i}^{s} \cdot N_{i}^{p}\right)\right\}\right) = O\left(k \cdot (N_{M}^{r})^{2} \cdot N_{i}^{p}\right)$$

which is polynomially bound to the number of jobs in the system, the number of slices for  $J_i$ , the number of rows the matrix, and the number of processors for  $J_i$ .

## 3.2.5 Multi-row Scheduling Algorithm

The next major modification involves generating the configurations for scheduling  $J_i$ ; each is evaluated using the fitness function, and the best is chosen. The goal here is to maximize the overall progress of *all* the jobs for a single iteration based on the principle that this measure leads to best average turnaround time.

The number of possible configurations to generate and evaluate its "fitness" is the same as an  $N_i^p$ -combination of the set of processors in the system. The size of this set is  $N_S^p$ , so the number of configurations is " $N_S^p$  choose  $N_i^p$ " with the following complexity [14]:

$$\begin{pmatrix} N_{S}^{p} \\ N_{i}^{p} \end{pmatrix} = \frac{N_{S}^{p}!}{N_{i}^{p}! \cdot (N_{S}^{p} - N_{i}^{p})!}$$

$$= \frac{N_{S}^{p}(N_{S}^{p} - 1) \cdot \cdot \cdot (N_{S}^{p} - N_{i}^{p} + 1)}{N_{i}^{p}(N_{i}^{p} - 1) \cdot \cdot \cdot 1}$$

$$= \left(\frac{N_{S}^{p}}{N_{i}^{p}}\right) \left(\frac{N_{S}^{p} - 1}{N_{i}^{p} - 1}\right) \cdot \cdot \cdot \left(\frac{N_{S}^{p} - N_{i}^{p} + 1}{1}\right)$$

$$\geq \left(\frac{N_{S}^{p}}{N_{i}^{p}}\right)^{N_{i}^{p}}$$

which is exponential in  $N_i^p$ . It is computationally intractable to generate all possibilities (particularly when  $N_i^p = N_S^p/2$ ), so we designed a pruned, polynomially-bound search algorithm to reduce

the complexity. This algorithm generates an initial set of processors for a target row from the trace matrix, and then selects processors from the other possible rows that match these as closely as possible. We first describe the input to the algorithm, followed by details of the principles used to guide the selection of processors and rows.

## **INPUT**

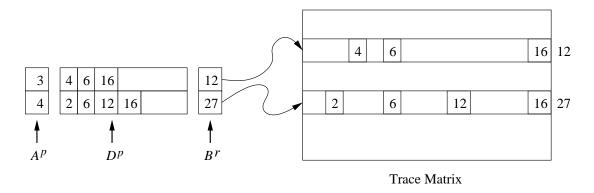

The input to this algorithm is a condensed version of the trace matrix that has only the "useful" rows—those that have  $N_i^p$  processors free. (Any other rows cannot possibly be assigned.) This information is generated by another function and is stored in a set of two vectors and two matrices, one set for processor information and another for row information. The vectors  $A^p$  and  $A^r$  store the number of processors that are free in the row corresponding to position  $A_i^p$  and the number of rows in which the  $j^{th}$  processor occurs, respectively. The matrix  $D^p$  stores the indexes of the processors unused in these rows. The matrix  $D^r$  stores the indexes of the rows the  $j^{th}$  processor is unused. These two variables have back-mapping vectors  $B^r$  and  $B^p$  to refer to the row and processor index corresponding to the positions in the first two vectors. Figure 3.2 shows an example of the relationship between two rows in  $D^p$  and the trace matrix.

#### **GUIDING PROCESSOR CHOICES**

The first step involves generating a combination of processors for the target row  $(R_t)$  used later. Intuitively, a processor free in many useful rows is likely to result in an efficient configuration because migration occurs less frequently. Accordingly, we rank the processors in decreasing order based on how many rows they occupy, which is stored in  $A^r$ . If all processors are considered, the algorithm is intractable. However, if only the first  $N_i^p$  processors are then selected, there is no allowance for variability, and a potentially good choice may be pruned prematurely. Let the variable  $\alpha$ , which we pass as an algorithm parameter, be the number of additional processors that are included beyond the first  $N_i^p$  processors. As  $\alpha$  decreases, the value is reduced, and the complexity on the number of combinations also decreases. However, a value that is too low may eliminate too

Figure 3.2: Picture of the relationship between  $A^p$ ,  $D^p$ ,  $B^r$  and the trace matrix. The job  $J_i$  needs 3 processors from two rows in the trace matrix. Only rows  $R_{12}$  and  $R_{27}$  contain enough processors, and the rest are ignored. The processor indices  $P_4$ ,  $P_6$  and  $P_{16}$  from  $R_{12}$  are stored in  $D_1^p$  and the indices  $P_2$ ,  $P_6$ ,  $P_{12}$  and  $P_{16}$  from  $P_{12}$  in  $P_2^p$ .  $P_1^p$  contains 3 because there were three processors from  $P_{12}$ , and  $P_1^p$  contains the number of processors indices were used from  $P_2^p$ .

many potentially good combinations from consideration. Currently, we set  $\alpha=2$ . The processors not included in the top  $N_i^p + \alpha$  are removed from  $D^p$ . Note that removing a processor from  $D_k^p$  may potentially result in  $A_k^p < N_i^p$ , whereupon that entire row is also removed from  $D^r$ .

Out of these  $N_i^p + \alpha$  possible processors, combinations of  $N_i^p$  are selected for  $R_t$ . There are  $O\left((N_i^p+2)^2\right) = O\left((N_i^p)^2\right)$  such combinations. The next task is to find  $N_i^s-1$  rows from the remaining "useful" rows with processors that closely match the combination of processors in  $R_t$  (to avoid excessive migration).

#### GUIDING PROCESSOR MATCHES

The basic idea is that given a selection of processors for  $R_t$ , the combination of processors selected from any other row in  $D^p$  is matched as closely as possible to  $R_t$ . Due to the sorting and pruning process described in the previous section, the value of  $\alpha$  already limits how different the processors can be between these two rows.

The algorithm starts with  $R_t$  and performs an initial scan through the remaining rows in  $D^p$ . For each row  $R_j$ , all the processors in it are compared with the processors in  $R_t$ . All the matches are saved in a vector M, and all the other processors are saved as alternatives in a vector W. If after the comparison with  $R_j$ ,  $N_i^p$  matching processors were found, this row and processor information is saved as part of the configuration for  $J_i$ . Otherwise, the processors from W are combined with the contents of M and saved as an alternative row.

If at the end of this scan there are  $N_i^s$  rows with an exact match, the algorithm immediately tests the configuration using the fitness function. Otherwise, there are  $x < N_i^s$  such rows, and the alternative rows generated during the initial scan are sorted in decreasing order based on how many of their processors match with those in  $R_t$ . The best  $N_i^s - x$  are selected and included in the configuration. Then the complete configuration is tested using the fitness function. The configuration with the best fitness measure is the one that the scheduler uses when scheduling  $J_i$ .

This strategy enables very controlled migration because any task that migrates from its processor in row  $R_t$  to a different one in another row must return to its original processor when the scheduler returns to  $R_t$ . The simulator was implemented such that any tasks that do not need to migrate stay on the same processor. This decision limits overhead and makes the encoding more elegant.

### TIME COMPLEXITY FOR THE COMPLETE ALGORITHM

The target row  $R_t$  is selected from  $D^p$  at most  $N_M^r$  times, each with  $O\left((N_i^p)^2\right)$  processor combinations. There are  $O\left(2N_S^p\right)$  comparisons between each  $R_t$  and at most  $N_M^r$  other rows. Any alternative rows are sorted in  $O\left((N_M^r)^2\right)$  steps after all of the processor comparisons. At each combination, the configuration is evaluated using the fitness function, so the time complexity of the complete algorithm is:

$$O\left(N_{M}^{r}\cdot(N_{i}^{p})^{2}\cdot\left((N_{M}^{r}\cdot2N_{S}^{p})+(N_{M}^{r})^{2}\right)\cdot T_{f}\right)=O\left((N_{M}^{r})^{2}\cdot(N_{i}^{p})^{2}\cdot(N_{S}^{p}+N_{M}^{r})\cdot T_{f}\right)$$

This algorithm is therefore polynomially bound to the number of jobs in the system, the number of rows in the trace matrix and the number of processors for  $J_i$  and in the system.

### 3.3 GANG SCHEDULING PERFORMANCE

We ran the modified Schark simulator on several mixtures of jobs to test the effectiveness of I/O awareness on performance. The simulated architecture was a mesh with 128 nodes, and the hard time limit was set to 80,000 simulated time units (STU), a sufficiently high number so that all of the jobs finished. There were 100 jobs, where each had 200 STU of computation to finish, and all of them were introduced at startup. (Separate tests with jobs arriving uniformly produced largely similar results.) Each time slice had the duration of 20 STU. The jobs did not perform any synchronization apart from the communication events. All of the jobs cycled through a pattern of nearest-neighbor, gather and scatter types of communication. The duration to access the disk was set to two STU. The value of  $N_i^{iters}$ , the number of iterations the job cycles through, was set to 100 for the first set of tests, but was modified later to simulate different I/O frequencies, as will be described in Section 3.3.3. Our parameter settings were loosely based on our experience implementing an out-of-core iterative PDE solver on an IBM SP2.